Ensuring Robust Performance: HIL Testing for Real-World Scenario Validation

Hardware-in-the-loop (HIL) testing has become a potent technique for verifying real-world scenarios in embedded systems, allowing engineers to replicate a variety of conditions that hardware and firmware will face in the field.

Ensuring dependable and efficient performance is a top priority. Businesses can improve resource efficiency, decrease field failures, and increase system reliability by incorporating HIL testing into the development process.

Soujanya Annapareddy has contributed to the development of scalable HIL testing frameworks that ensure inbuilt systems meet demanding performance standards. Her work includes simulating real-world conditions, conducting stress testing and failure mode analysis, and automating testing scenarios like power fluctuations, network disruptions, and thermal variations.

By integrating HIL testing into development pipelines, she has helped enhance product quality through improved firmware validation and the construction of extensive testbeds for parallel device testing.

The impact of HIL testing at the organizational level is concrete and measurable. Thanks to Annapareddy's contributions, automated HIL testing has led to a significant reduction in testing time and a significant reduction in validation cycles.

Early identification of firmware and hardware problems has reduced field failures by 30%, increasing product reliability after deployment.

Increased test coverage has been achieved by simulating real-world conditions, improving validation accuracy by 50%.

The implementation of scalable HIL testbeds has led to cost savings by reducing reliance on physical prototypes, while real-time monitoring dashboards have accelerated debugging and issue resolution, improving overall efficiency.

Throughout her career, Annapareddy has initiated a number of significant initiatives that have improved firmware testing and validation procedures.

She designed and deployed scalable HIL frameworks for embedded systems so that firmware resilience under fluctuating power conditions, network disruptions, and extreme environmental factors.

Her contribution to the integration of automated firmware testing into CI/CD pipelines also significantly improved system reliability and reduced release cycles by 25%.

Her expertise in real-time operating systems (RTOS) and driver validation has contributed to improved peripheral communication, while model-based testing approaches have allowed scenario-driven test case generation, optimizing firmware performance prior to deployment.

The results of these efforts have been evident and transformative.

Automated firmware validation has cut testing cycles by 40%, while structured stress and power cycle testing have improved long-term firmware stability by 35%. Scalable test setups have led to a 20% reduction in lab costs, further maximizing resource use.

Debugging efficiency has been considerably enhanced, with real-time monitoring reducing defect triage time by 60%, accelerating overall issue resolution, and increasing system reliability.

The challenges faced in firmware validation have been considerable, but Annapareddy has successfully addressed critical issues that hinder efficient development. By integrating HIL and software-in-the-loop (SIL) testing, she has achieved firmware compatibility across multiple hardware platforms, overcoming system resilience concerns.

The automation of test scripts and integration into CI/CD pipelines has greatly shortened traditionally lengthy validation cycles, while continuous monitoring and structured logging have improved defect detection and resolution rates.

These solutions have paved the way for faster deployments, fewer post-deployment failures, and enhanced firmware performance in mission-critical systems.

Her contributions extend beyond technical execution, with her research paper, "Advancements in Firmware Testing and Validation Techniques," published in September 2024, highlighting the evolution of firmware testing methodologies.

The paper explores the transition from traditional validation approaches to advanced HIL, SIL, and model-based testing frameworks, analyzing the role of RTOS, OTA updates, and structured validation in modern embedded systems.

By providing insights into CI/CD adoption, the research contributes to optimizing firmware development lifecycles and improving overall reliability.

It appears that there will be major developments in HIL testing in the future. Automation-driven validation will continue to gain prominence, with HIL, SIL, and CI/CD pipelines streamlining firmware testing and deployment.

The increasing complexity of embedded systems will necessitate more structured RTOS and peripheral validation methods, ensuring seamless hardware-software integration.

The development of structured debugging methods and real-time monitoring will speed up and improve defect resolution procedures, which will ultimately result in more stable firmware.

Automated testing, simulations of real-world situations, and scalable validation infrastructures that accommodate future expansion are essential for businesses to keep a competitive edge.

Incorporating HIL testing into firmware validation has reshaped embedded system development by guaranteeing stability, effectiveness, and dependability in practical applications.

With professionals like Soujanya Annapareddy promoting this field's innovation, businesses can take advantage of these developments to create reliable, cutting-edge embedded systems that perform well in real-world scenarios.

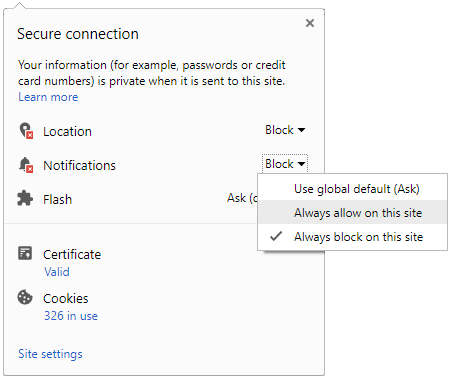

Click it and Unblock the Notifications

Click it and Unblock the Notifications