Sandra Shaji Reveals How DTCO is Revolutionizing Sub-2nm Semiconductor Design & Manufacturing

Samsung's Sandra Shaji discusses Design-Technology Co-Optimization (DTCO) for sub-2nm semiconductors. Her pioneering work builds infrastructure to ensure advanced chips are manufacturable, efficient, and reliable, addressing critical challenges in power delivery and interconnects. This is vital for future AI, automotive, and IoT systems, ensuring innovation meets manufacturing realities.

As artificial intelligence, automotive autonomy, and connected devices continue to accelerate demand for compute, the semiconductor industry is entering a phase where efficiency and manufacturability matter as much as raw performance. At technology nodes below 2 nanometers, the traditional assumptions that guided chip design for decades no longer hold. Power delivery, clock stability, and interconnect behavior have become first-order design constraints, directly influencing whether advanced chips can be manufactured reliably at scale and deployed across national critical industries.

This shift has placed renewed focus on design–technology co-optimization, or DTCO, the discipline that aligns device physics, interconnect architecture, and design enablement from the earliest stages of node development. Sandra Shaji, an engineering leader working as a Senior Engineer at Samsung working at the forefront of advanced semiconductor research, and an editorial board member at the Sarcouncil Journal of Engineering and Computer Sciences, has built her career around this inflection point, developing early infrastructure that allows next generation technologies to be evaluated before costly commitments are made.

AI-generated summary, reviewed by editors

"As chips become smaller and more complex, even minor design assumptions can cause major failures in performance, power consumption, or yield," she explains. "The core challenge is closing the gap between what designers want to build and what can actually be manufactured at advanced nodes."

The End of Ring Oscillators as a Proxy for Reality

For years, the industry relied on transistor-level metrics and simple ring oscillator simulations to estimate performance and power. That methodology remained effective through the 7-nm node, where simplified ring-oscillator models with coarse interconnect parasitics adequately represented full-chip behavior. Beyond this point, parasitics, routing congestion, metal pitch limits, and lithography constraints fundamentally altered the design landscape.

At advanced nodes, the feasibility of using backside metals for power, clock, and even signal delivery often becomes the deciding factor in achieving routability and meeting aggressive area targets, with direct implications for performance and yield, and cell to BEOL co-optimization determine whether performance gains are even achievable. Sandra’s work focuses on building the infrastructure that allows these variables to be explored together, rather than in isolation.

Her DTCO infrastructure development for sub-2nm technology created a unified environment where device architectures, routing strategies, and power delivery methods could be rapidly prototyped and evaluated. By automating layout processing, LVS, RC extraction, and characterization across multiple EDA tools, she enabled design teams to assess power, performance, and area tradeoffs in under two weeks, a process that previously required months and delivered far less accuracy.

Recent advances in process design kit (PDK) generation have further enhanced this capability. By streamlining the conversion of foundry process data into usable PDKs, designers can now incorporate more accurate transistor, interconnect, and parasitic models earlier in the workflow. This integration allows for faster verification of power and performance assumptions within DTCO frameworks, ensuring that design decisions are informed by realistic manufacturing parameters rather than simplified models. Sandra leveraged these improvements in PDK methodology to strengthen her infrastructure, enabling teams to iterate on sub-2nm designs with confidence in both manufacturability and performance fidelity.

"Once scaling pushed into these regimes, transistor metrics alone stopped telling the truth," she says. "You need to understand how wiring, clocking, and power interact with the cell architecture as a system."

Backside Power Delivery as a First-Order Design Constraint

Backside power delivery is more than a technical optimization. By relocating power routing to the backside of the wafer, designers can reduce congestion, improve IR drop and supply integrity, and unlock performance gains while improving interconnect power delivery without exacerbating frontside routing congestion. These benefits translate directly into energy efficiency for AI accelerators, automotive processors, and IoT devices, all of which are critical to national competitiveness and domestic manufacturing goals.

Sandra’s work supports early evaluation of backside PDN strategies alongside backside clock routing and BEOL choices, ensuring that power efficiency gains do not come at the cost of yield or manufacturability. This balance is essential as governments and industry push to localize advanced chip production and reduce dependency on fragile global supply chains.

"Manufacturability has become a strategic concern," she notes. "If a technology cannot be built reliably at scale, it does not matter how impressive the performance numbers look on paper."

Design–Technology Co-Optimization as Risk Reduction

One of the most significant impacts of DTCO is risk reduction. At advanced nodes, late-stage failures can cost billions of dollars and years of lost time. Sandra’s infrastructure allows foundries and design teams to surface issues early, when changes are still affordable.

By integrating resistivity and capacitance modeling of interconnect layers with full PPA sweeps, her framework provides a more accurate picture of how design choices will behave in silicon. This early feedback loop prevents entire technology directions from failing late in development.

From Academic Research to Production-Grade Infrastructure

Sandra’s perspective is shaped by both academic and industrial experience. During her graduate research, she contributed to 3nm GAA-FET PDK development and explored 3D IC placement, laying the foundation for her later work in automation and large-scale design exploration.

That blend of theory and practice continues to inform her contributions today. She also serves as a reviewer for IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, helping shape how the field evaluates new methodologies for advanced node design.

"The goal is not just innovation," she emphasizes. "It is innovation that can survive the realities of manufacturing, power constraints, and long-term scalability."

Building the Invisible Backbone of Advanced Chips

Much of the most critical semiconductor work happens far from consumer view. Backside power delivery, clock tree routing, and DTCO infrastructure rarely make headlines, yet they determine whether advanced chips can meet the energy efficiency and reliability demands of modern computing.

Sandra’s work exemplifies this hidden backbone. By enabling early, data-driven exploration of sub-2nm technologies, she helps ensure that future AI, automotive, and IoT systems are not only powerful, but manufacturable, efficient, and resilient.

"As scaling continues, success depends on getting the fundamentals right early," she says. "If we do that, everything built on top becomes possible."

Her contributions highlight how foundational engineering decisions, made years before production, shape the technological capabilities that economies and societies ultimately depend on.

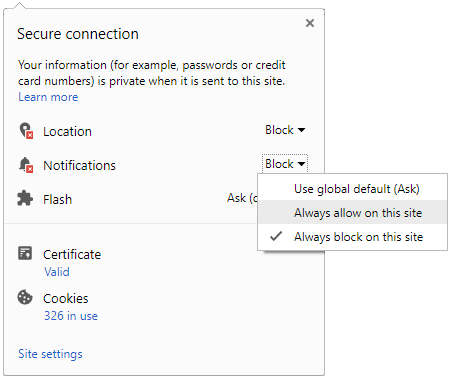

Click it and Unblock the Notifications

Click it and Unblock the Notifications